@@@電路圖@@@

1.前置作業:

下載Quartus II(用來撰寫Verilog HDL語言程式)

下載ModelSim (用來跑出CRC波形的程式)

2.建立專案:

-1.創一個新專案(xxx.QPF檔)

-2存放路徑

紅色框框:存放專案與程式碼和模擬結果的資料夾(可自行建立)

藍色框框:專案名稱(注意:需與程式碼內的開頭model crc-16

一樣名稱)

-3撰寫程式碼(XXX.v檔)使用Verilog HDL語言

-4編譯程式(成功之後會跳出successful的提示視窗)

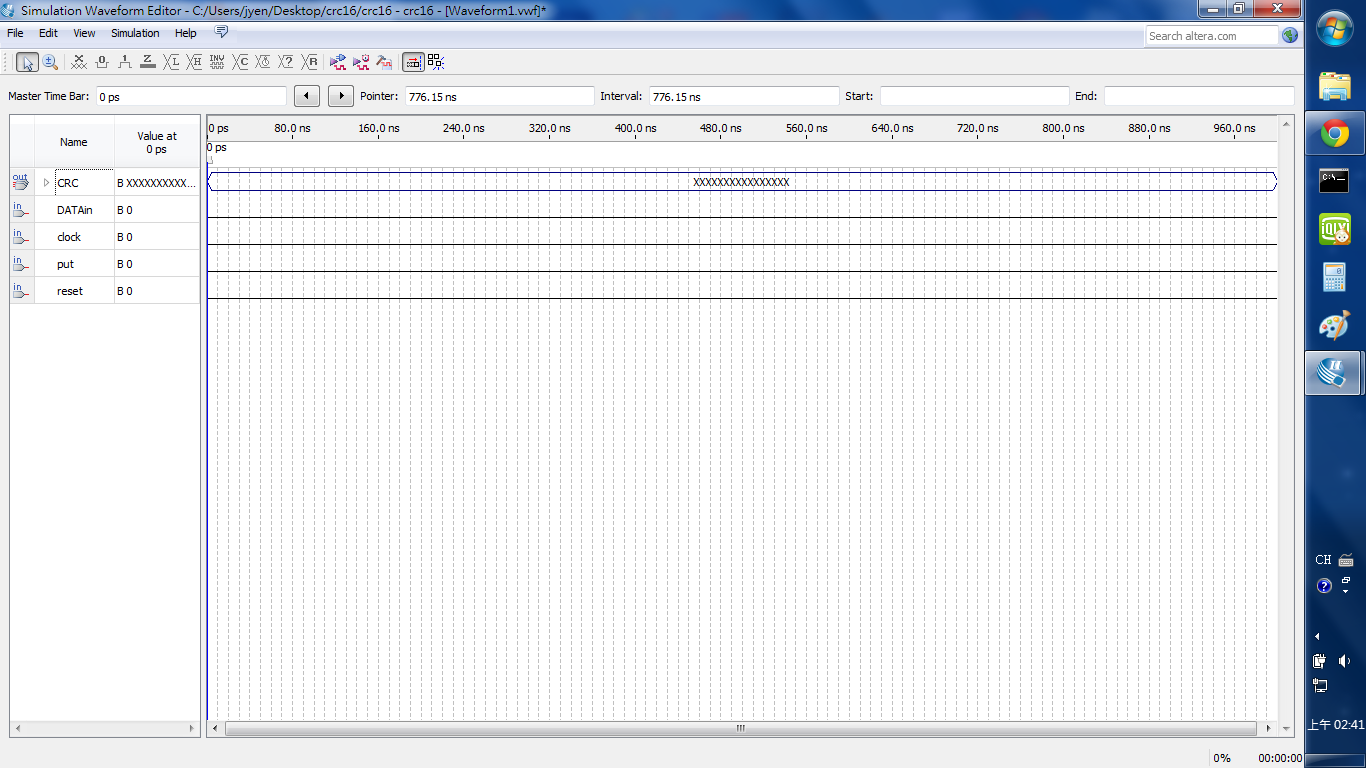

-5建立模擬波形檔

第一步:插入程式碼內的Reg和clock等等模擬設定

第二步:點選列出清單

第三步:選擇插入元件

第四步:全部移入到模擬設定

-6設定初始值

紅色區:可設定電壓高低(選取區段波形可設定部分高電壓或

低電壓;紅色區右邊有個C鈕可以直接產生一個clock)

紫色鈕:開始模擬

<註:此程式碼設定datain為資料[01]以clock正緣觸發(0-1之間

觸發),當put進來(put==1)才視作有data進來,reset為致0

鈕 >

-7ModelSim模擬結果圖

此文章為本作者撰寫,若有引用請標明來源出處

沒有留言:

張貼留言